0.简介

P2P接口是一种双向握手接口,传输的前级和后级各提供一个数据有效信号valid和忙信号busy信号,只有当两个信号达成某种指定情况时,握手完成,数据传输完成,否则数据传输均未完成。这可以看成一种分布式控制方式,每个模块的开发人员仅需要考虑上下级的握手信号即可。

1.端口

| 端口名 | 类型 | 位宽 | 功能 |

|---|---|---|---|

| din_valid | input | 1 | 输入数据有效信号 |

| din_busy | output | 1 | 输入部分忙,不接受输入数据 |

| dout_valid | output | 1 | 输出有效信号 |

| dout_busy | input | 1 | 输出部分忙,下一级不接受输入 |

| din | input | - | 输入数据 |

| dout | output | - | 输出数据 |

2.状态分析

2.1.输入状态分析

| din_valid | din_busy | 状态 |

|---|---|---|

| 0 | 0 | 静默,无数据传输 |

| 1 | 0 | 正常接收数据,无阻塞情况发生 |

| 0 | 1 | 输入忙,但无数据输入 |

| 1 | 1 | 输入数据被阻塞 |

2.2.输出状态分析

| dout_valid | dout_busy | 状态 |

|---|---|---|

| 0 | 0 | 静默,无数据传输 |

| 1 | 0 | 正常发送数据,无阻塞情况发生 |

| 0 | 1 | 输出忙,但无数据输出 |

| 1 | 1 | 输出数据被阻塞 |

2.3.组合情况分析

| din_valid | din_busy | dout_valid | dout_busy | 状态 |

|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 全阻塞 |

| 1 | 0 | 1 | 1 | 接收在本级被阻塞的数据 |

| 1 | 1 | 1 | 0 | 释放被阻塞被本级的数据 |

3.结构框图

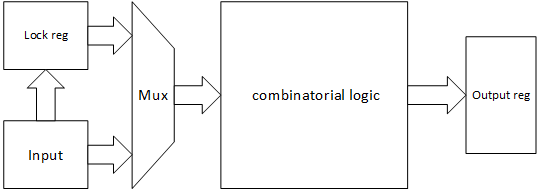

3.1.结构

- Input:数据输入接口

- Lock reg:输入锁存器,当阻塞时在本级存储被阻塞的数据

- combinatiorial logic:处理逻辑,用于处理输入数据

- output reg:输出寄存器

3.2.分析

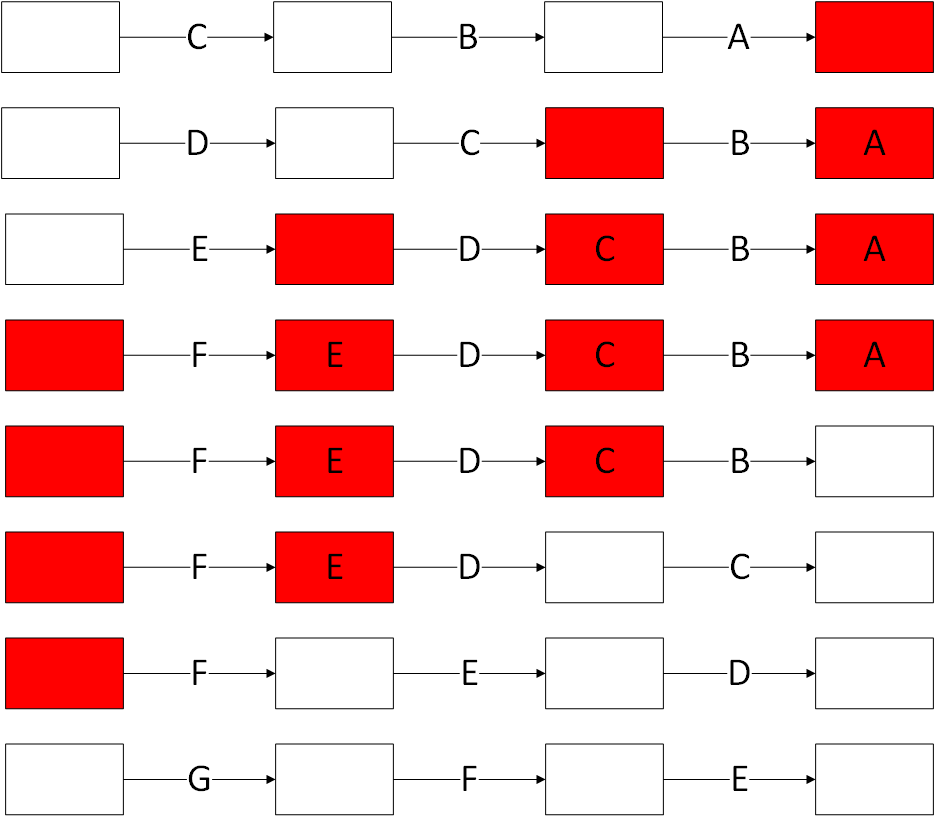

下图分析了一个在四级流水线中数据的传输过程,其中:

- 白色的方块表示正常工作没有阻塞的模块

- 红色的方块表示阻塞的模块(dout_busy=1)

- 箭头上的数据表示在上一个模块输出的数据

- 方块中的数据表示被存储在模块中的数据

分析过程如下:

- 最后一级dout_busy=1,din_busy=0,则刚遇到阻塞,将上一级输入存储在本级lock reg中

- 最后一级din_busy=1,即第三级dout_busy=1,此时数据B已经位于第三级output reg中,第三级将输入数据C存储在第三级的lock reg中

- …

- 当最后一级dout_busy=1且din_busy=0时,下一级阻塞解除,第四级output reg中的数据已经被之后接收

- 最后一级din_busy=0即第三级dout_busy=0时,第四级阻塞解除,原先存储在第四级lock reg中的数据A已经被送到output reg中传送到下一级,同时接收存储在第三级output reg中的数据B

- 第三级din_busy=0即第二级dout_busy=0时,第三级阻塞解除,原先存储在第三级lock reg中的数据C被送到output reg中传送到下一级,同时接收存储在第二级output reg中的数据D

- …

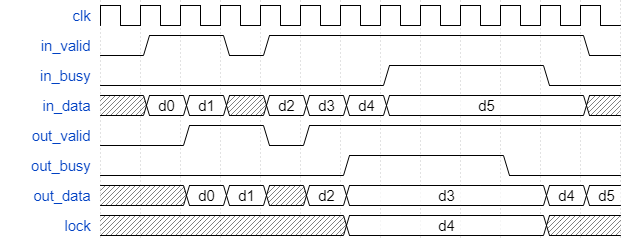

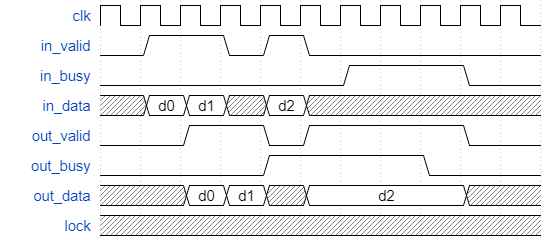

3.3.时序图分析

上图为一个通常情况的可用于流水线的P2P接口时序图,当连续传递无阻塞时(d0和d1),busy信号复位,valid信号和数据相对于上一级延迟一个时钟周期。d2~d5表示的是在流水线过程中发送后级阻塞的处理方法:

- 当后级流水线发生阻塞时,该阻塞在一个时钟周期后反馈到前级

- 由于前级反馈产生busy信号由后级busy信号寄存产生,而后级的输出由前级输出寄存(处理)产生,因此两个busy信号之间差了两个数据(前级卡在端口的数据为d5,而后级卡在端口的数据为上上个数据d3)

- 由于相差两个数据,则需要一个深度为1旁路缓存暂存中间的数据d4

- 当后级busy信号复位后,完成未完成传输d3后,立刻从旁路缓存中取出d4进行传输,此时前级的数据d5完成传输,在下一个时钟周期由后级转发

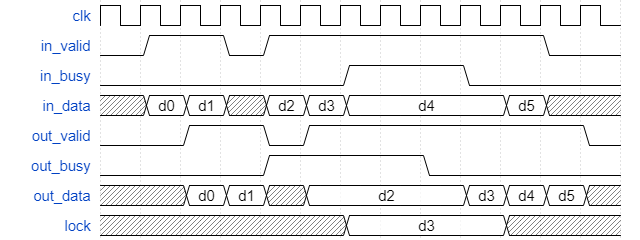

上图是传输开始时就有后级busy信号的情况,可以发现,该情况与上一种情况相同,参照上一种情况可分析。

上图是仅传输一个单独数据且遇到阻塞的情况,该情况最大的不同是din_valid信号仅置位一个时钟周期,而dout_valid要等发送数据d2完成发送后再复位,因此两个valid信号之间并不是简单的延迟一个周期的关系。

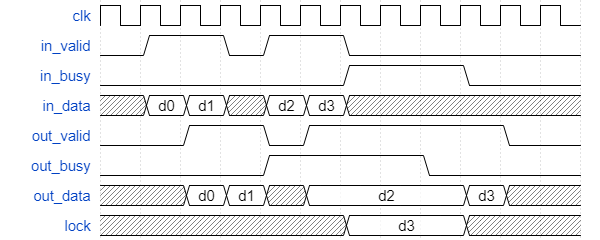

上图是最后一个典型情况——仅发送两个数据且遇到阻塞的情况:

- 前级发送第一个数据d2时,后级阻塞,但是由于后级无传输行为,因此不阻塞该传输

- 后级接受到数据d2,并发生阻塞情况,同时后级的阻塞还未传输到前级,此时前级发送数据d3

- 后级发送数据d2未完成,但前级d3发送已经完成,因此d3被存入旁路缓存,等待发送,同时前级静默

- 后级发送d2完成时,从旁路缓存中取出数据d3进行发送

4.实现细节

首先定义了一些用于简化判断的wire型变量:

1 | wire busy_drop_buf = (!dout_busy) && din_busy ; |

busy_drop_buf表示dout_busy信号下降沿,该信号在后期判断中经常使用;is_din_busy表示后级发生阻塞行为,当后级的valid和busy同时置位时,表示后级有数据未完成传输,此时阻塞信号应传递到前级;is_no_dout表示没有数据需要发送,即旁路缓存中没有数据且上一级没有发送给这一级的数据;is_lock和is_unlock分别表示数据存入旁路缓存和数据从旁路缓存中取出,其中:

- is_lock:当后级发生阻塞(is_din_busy)且尚未传到前级完成一次数据传输((!din_busy) && din_valid)时有效,即后级发生第一个阻塞时将前级发送的数据放到旁路缓存中(该数据不做特殊处理会丢失)

- is_unlock:当后级阻塞接触的第一个周期(busy_drop_buf)完成后,若缓存中有数据,则取出发送

4.1.旁路缓存

旁路缓存用于在打断busy反馈的组合路径且不丢失数据,该部分分为两个信号:

- lock_data:缓存数据,用存储数据

- lock_valid:缓存有效,用于标记lock_data中的数据是否有效

1 | always @ (posedge clk or negedge rst_n) begin |

这两个信号控制基本相同,通过is_lock和is_unlock分别进行进缓存和出缓存控制。

4.2.dout_valid

由上分析,当上一级传输完成时,需要将上级传输来的数据转发给下一级,此时dout_valid信号置位;当当前传输完成且没有需要发送的数据时,后级没有需要发送的数据,dout_valid信号复位,代码如下所示:

1 | always @ (posedge clk or negedge rst_n) begin |

4.2.din_busy

din_busy信号由寄存器产生,因此可以打断从最后一级向前传递的组合逻辑busy反馈路线,当后级发生阻塞时,前级不能继续发送数据,此时该信号置位;当后级busy信号复位后,无论是否发送数据,均可接收新数据(参考时序图分析),因此当后级busy信号复位后该信号复位。

1 | always @ (posedge clk or negedge rst_n) begin |

4.3.dout_data

dout_data信号为转发数据,有三种情况:

- 后级阻塞(is_din_busy):阻塞情况下,输出数据不能改变

- 释放缓存(is_unlock):达成缓存释放条件,此时从缓存中取出数据发送

- 其他情况:发送前级传递来的数据

整体代码如下所示:

1 | always @ (posedge clk or negedge rst_n) begin |