APB学习笔记

APB简介

The APB is part of the AMBA 3 protocol family. It provides a low-cost interface that is optimized for minimal power consumption and reduced interface complexity.

The APB interfaces to any peripherals that are low-bandwidth and do not require the high performance of a pipelined bus interface. The APB has unpipelined protocol.

All signal transitions are only related to the rising edge of the clock to enable the

integration of APB peripherals easily into any design flow. Every transfer takes at least

two cycles.

The APB can interface with the AMBA Advanced High-performance Bus Lite

(AHB-Lite) and AMBA Advanced Extensible Interface (AXI). You can use it to provide

access to the programmable control registers of peripheral devices.

APB是AMBA总线的组成部分,特点有:

- 面向低功耗,低带宽应用(当然,性能和传输速度低)

- 非流水线设计

- 仅依赖时钟上升沿,每次传输最少需要两个时钟周期

APB可作为AHB-Lite和AXI总线的对外低速接口

写数据

非等待模式

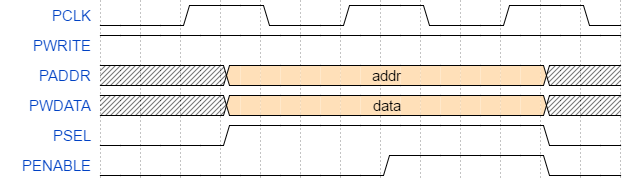

The write transfer starts with the address, write data, write signal and select signal all changing after the rising edge of the clock. The first clock cycle of the transfer is called the Setup phase. After the following clock edge the enable signal is asserted, PENABLE, and this indicates that the Access phase is taking place. The address, data and control signals all remain valid throughout the Access phase. The transfer completes at the end of this cycle.

非等待模式认为系统一直都是准备好的,因此不需要关心设备当前状态,非等待模式分为两个部分:

- 建立部分:准备好数据(PWDATA),地址(PADDR)和并拉高需要传输信号外设的片选线(PSEL)

- 传输部分:拉高使能线(PENABLE),进行传输

传输完成后,拉低PSEL和PENABLE,完成传输,波形图如下所示

等待模式

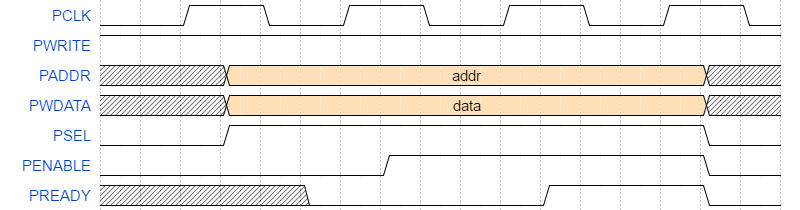

During an Access phase, when PENABLE is HIGH, the transfer can be extended by driving PREADY LOW.

等待模式引入从机状态信号PREADY,当使能信号PENABLE有效时,传输开始,并持续到PREADY信号拉高。当PREADY信号未被拉高时,所有信号保持不变。其他传输过程与非等待模式相同

读数据

非等待模式

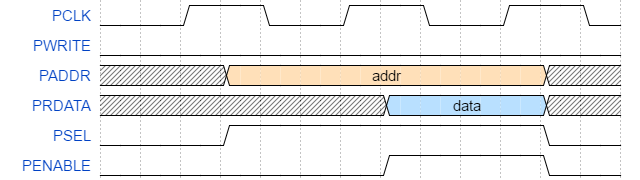

在非等待模式中,认为从机在一个时钟周期内就能送出数据,与写数据相同分为两个模式:

- 建立部分:准备好地址(PADDR)和并拉高需要传输信号外设的片选线(PSEL)

- 传输部分:拉高使能线(PENABLE),进行传输(在这个时钟沿之前从机要将数据送到数据总线PRDATA上)

传输完成后,拉低PSEL和PENABLE,完成传输,波形图如下所示

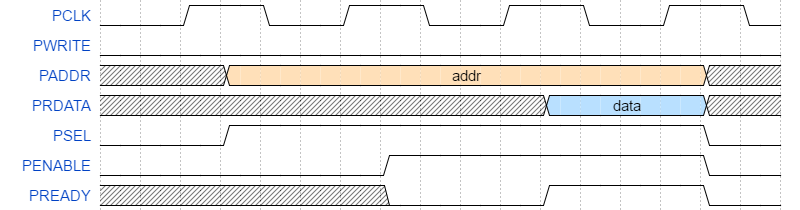

等待模式

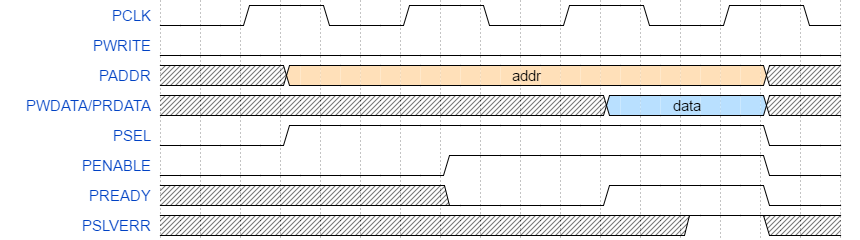

等待模式中,从机无法在一个时钟周期内准备好数据,则当数据未准备好时,拉低PREADY信号,传输即被”卡住“,所有由主机控制的信号都不发生变化,直达从机准备好数据,将PREADY拉高,波形如下:

错误报告

当传输发生错误时,从机拉高错误报告信号线PSLVERR,该信号会被APB桥映射到AXI或AMBA总线上,由AXI/AMBA总线的主机进行处理。系统仅关心在APB传输周期最后一个时钟周期的值。

错误报告信号线PSLVERR在系统中并不是必须的。波形如下

系统状态转移与信号说明

系统状态转移

系统状态图如下:

- IDLE:初始状态,也是等待传输状态。当片选信号PSELx拉高时总线请求通信,进入SETUP状态

- SETUP:建立状态,主从机在该状态准备好所有数据,并进入ACCESS状态

- ACCESS:传输状态,拉高PENABLE信号

- 当PREADY信号拉高,传输完成,根据是否有下一次传输(PSELx是否为高),进入IDLW状态后SETUP状态

- 当PREADY信号为低,数据未准备好,在ACCESS状态等待PREADY信号拉高

端口说明

| 信号名 | 来源 | 说明 |

|---|---|---|

| PCLK | 时钟源 | 系统时钟,传输发生在上升沿 |

| PRESETn | 复位源 | 复位信号,低使能 |

| PADDR | APB桥 | 地址信号,最高可达32位 |

| PSELx | APB桥 | 片选信号,表示x从机是否被选中 |

| PENABLE | APB桥 | 使能信号,标记传输使能 |

| PWRITE | APB桥 | 读/写控制信号,高位写,低为读 |

| PWDATA | APB桥 | 写数据 |

| PREADY | 从机 | 标记从机是否已将数据发送到总线,高为ready |

| PRDATA | 从机 | 读数据 |

| PSLVERR | 从机 | 故障信号,高为发生故障 |

疑问

如何判定在传输完成后是否有继续传输?